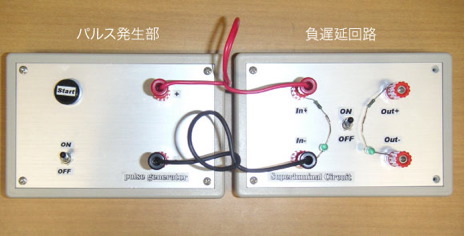

写真(全景)

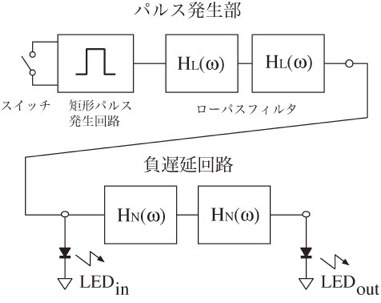

全体のブロック図

全体はパルス発生部と負遅延回路からなっている.パルス発生部ではスイッチを押すと同時にタイマICによって矩形パルスが発生し,それがローパスフィルタを通過することで,帯域制限された信号が出力される.負遅延回路では帯域制限された信号に対して負の遅延がもたらされる.

回路全体の詳細

回路定数

(抵抗の単位はすべてオーム,キャパシタの単位はすべてF,uはマイクロの意)

R0=6.8M, C0=0.22u, R1=2.2M, C1=0.22u, R2=10k, R3=2.2k, R=1M, C=0.22u, R'=10k, C'=22nF